RISC-V芯片:如何打造仿真到測(cè)試的完整驗(yàn)證閉環(huán)

RISC-V 的發(fā)展背景與全球趨勢(shì)

RISC-V 作為新一代開放指令集架構(gòu)(ISA),已經(jīng)從學(xué)術(shù)界的概念研究快速走向全球產(chǎn)業(yè)化浪潮。在短短數(shù)年內(nèi),它從“開源替代方案”成長(zhǎng)為全球半導(dǎo)體生態(tài)的重要力量,成為 CPU 架構(gòu)演進(jìn)中最具活力的選項(xiàng)之一。

全球崛起:從開源實(shí)驗(yàn)室到產(chǎn)業(yè)級(jí)生態(tài)

RISC-V 的核心優(yōu)勢(shì)來自其 開源、免費(fèi)、可擴(kuò)展、可裁剪 的本質(zhì),使其迅速獲得產(chǎn)業(yè)界認(rèn)可。

RISC-V International(原RISC-V基金會(huì))目前覆蓋 70 多個(gè)國(guó)家、超過 4000 名成員

生態(tài)成員包括:谷歌、英偉達(dá)、IBM、Qualcomm、阿里巴巴、三星、西部數(shù)據(jù)(WD)等全球科技巨頭,同時(shí)也吸引了大量初創(chuàng)企業(yè)與科研團(tuán)隊(duì)加入。

市場(chǎng)規(guī)模爆發(fā):進(jìn)入數(shù)十億級(jí)別的商業(yè)時(shí)代

過去十年中,RISC-V 從“驗(yàn)證階段”進(jìn)入“規(guī)模商用階段”,出貨量呈指數(shù)增長(zhǎng)。

全球市場(chǎng)預(yù)測(cè)

2025 年全球 RISC-V 芯片出貨量預(yù)計(jì)突破 20 億顆。2030 年有望達(dá)到數(shù)百億片規(guī)模,成為全球增長(zhǎng)速度最快的 CPU 架構(gòu)之一。其中約 50% 的增長(zhǎng)來自中國(guó),包括 AIoT、智能終端、邊緣計(jì)算、車規(guī) MCU 等廣泛場(chǎng)景。

AI 加速賽道成為增長(zhǎng)引擎

面向推理、訓(xùn)練、AI 算子加速的 RISC-V AI SoC 有望在未來 5–7 年內(nèi)達(dá)到數(shù)十億顆級(jí)別的市場(chǎng)規(guī)模。由于 RISC-V 可讓企業(yè)自由擴(kuò)展自定義指令(如矩陣運(yùn)算、向量引擎等),非常適合構(gòu)建 輕量級(jí)、高能效比的 AI 加速芯片。

技術(shù)競(jìng)爭(zhēng)格局:向 “X86 + Arm + RISC-V” 三足鼎立演變

RISC-V 的開放性和可擴(kuò)展性正在改變傳統(tǒng) CPU 的競(jìng)爭(zhēng)邏輯。全球 CPU 架構(gòu)正步入新的競(jìng)爭(zhēng)平衡點(diǎn)。隨著 RISC-V 的生態(tài)加速完善、工具鏈不斷成熟、商業(yè)化案例逐年增多,行業(yè)開始出現(xiàn)明確趨勢(shì):CPU 架構(gòu)體系正從“兩極格局”走向“X86 + Arm + RISC-V”三足鼎立的新階段。

RISC-V 時(shí)代的驗(yàn)證挑戰(zhàn)

從測(cè)試的角度看,RISC-V 與 x86 / Arm 的驗(yàn)證本質(zhì)上并無“架構(gòu)本身決定的難點(diǎn)差異”, 真正的差別在于:RISC-V 的靈活性遠(yuǎn)高于傳統(tǒng)架構(gòu),但行業(yè)尚缺乏成熟的工具鏈、案例和 SOP,因此“驗(yàn)證經(jīng)驗(yàn)不夠沉淀”。

因此,RISC-V 測(cè)試中普遍會(huì)遇到三個(gè)現(xiàn)實(shí)挑戰(zhàn):

(1)缺少可復(fù)用的驗(yàn)證流程

不同公司、不同項(xiàng)目、不同自定義 ISA 都有自己的驗(yàn)證方法,沒有形成像 Arm/x86 那樣的標(biāo)準(zhǔn)化路徑。

(2)缺少全過程的一致性測(cè)試驗(yàn)證

EDA 仿真一套語言,硅測(cè)一套語言,系統(tǒng)調(diào)試又是一套,結(jié)果常常無法連貫,一致性缺失。

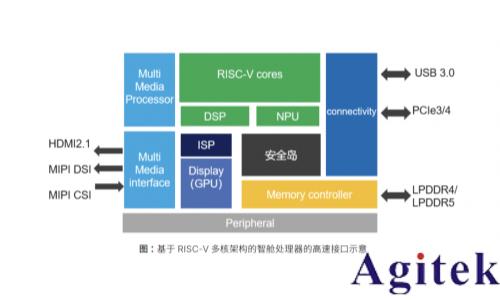

(3)缺少成熟的高速接口調(diào)試經(jīng)驗(yàn)

當(dāng) RISC-V 芯片開始進(jìn)入 AI、汽車、數(shù)據(jù)中心等高端場(chǎng)景,高速接口(PCIe、DDR、CXL、Ethernet)成為真正的痛點(diǎn)來源。

綜上所述,RISC-V 的驗(yàn)證難點(diǎn)不在于“架構(gòu)難”,而在于生態(tài)仍缺乏一條真正完整、協(xié)同、連貫的 End-to-End 驗(yàn)證鏈路——從前仿真,到半實(shí)物平臺(tái),再到硅測(cè)與系統(tǒng)級(jí)驗(yàn)證。

是德科技的完整驗(yàn)證方案

(從ADS仿真到后硅測(cè)試)

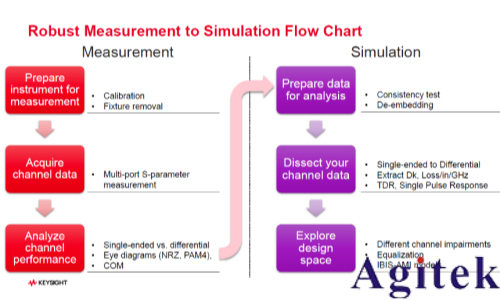

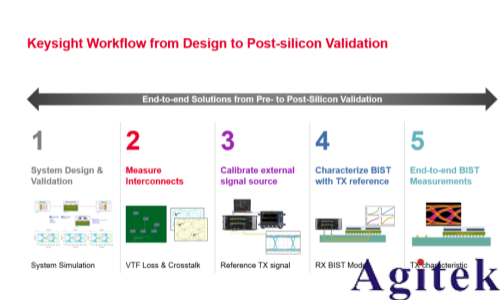

面對(duì)RISC-V芯片設(shè)計(jì)和驗(yàn)證的多重挑戰(zhàn),是德科技(Keysight)則是從仿真、半實(shí)物仿真、無源測(cè)試驗(yàn)證、有源測(cè)試、功能和系統(tǒng)測(cè)試,以及用相同的算法拉通全過程來加速這一過程。其核心理念是在產(chǎn)品開發(fā)全流程中形成“閉環(huán)”驗(yàn)證鏈路解決方案。下圖是PCB/Cable/Fixture設(shè)計(jì)和驗(yàn)證的仿測(cè)閉環(huán)流程實(shí)例。

圖:是德科技的PLTS物理層測(cè)試方案和ADS仿真軟件形成仿測(cè)閉環(huán)驗(yàn)證

在設(shè)計(jì)階段,是德科技的ADS (Advanced Design System) 等EDA仿真工具發(fā)揮關(guān)鍵作用。工程師可以利用ADS對(duì)高速接口電信道進(jìn)行信號(hào)完整性(SI)仿真、對(duì)電源分配網(wǎng)絡(luò)進(jìn)行電源完整性(PI)分析。例如,通過ADS的PIPro模塊可以仿真芯片/板級(jí)電源網(wǎng)絡(luò)的IR壓降和阻抗分布,預(yù)測(cè)不同去耦方案對(duì)電壓紋波的影響。對(duì)于PCIe、DDR、以太網(wǎng)等高速鏈路,則可在ADS中建立拓?fù)淠P停M(jìn)行時(shí)域與頻域仿真,評(píng)估插損、抖動(dòng)、眼圖裕量是否滿足標(biāo)準(zhǔn)要求。這些仿真能夠在設(shè)計(jì)初期階段發(fā)現(xiàn)潛在信號(hào)/電源問題,指導(dǎo)硬件布局布線和IP參數(shù)選型,避免走線不良或電源噪聲過大導(dǎo)致后期整改。

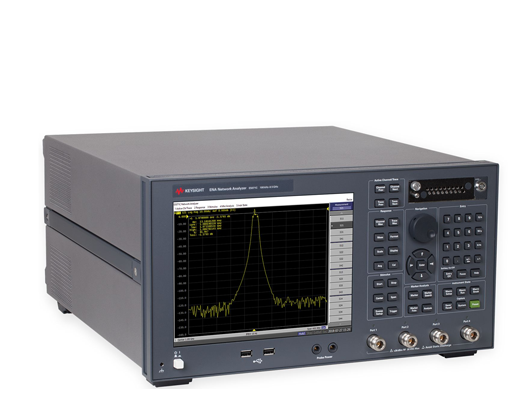

進(jìn)入產(chǎn)品實(shí)現(xiàn)階段后,是德科技提供一系列尖端測(cè)試測(cè)量設(shè)備,幫助工程師驗(yàn)證實(shí)際芯片和系統(tǒng)與仿真預(yù)期一致,完成最終的硅后驗(yàn)證。例如,使用超高帶寬實(shí)時(shí)示波器(如Keysight UXR系列)測(cè)量高速接口的發(fā)射信號(hào)眼圖和抖動(dòng),對(duì)比仿真得到的眼圖指標(biāo),驗(yàn)證設(shè)計(jì)裕量;利用矢量網(wǎng)絡(luò)分析儀(VNA)對(duì)封裝、PCB走線和連接器的S參數(shù)進(jìn)行測(cè)量,并通過去嵌技術(shù)除去治具影響,將實(shí)測(cè)信道特性與ADS仿真模型對(duì)應(yīng)比對(duì),從而校準(zhǔn)模型精度。同時(shí),是德科技的測(cè)試方案注重自動(dòng)化和相關(guān)性:許多儀器配套軟件可自動(dòng)執(zhí)行標(biāo)準(zhǔn)一致性測(cè)試,用腳本一次性跑完整套用例并生成報(bào)告;仿真結(jié)果和測(cè)量數(shù)據(jù)可以在同一平臺(tái)下關(guān)聯(lián)分析,幫助快速定位差異原因,實(shí)現(xiàn)設(shè)計(jì)與測(cè)試的無縫銜接。

通過將前端設(shè)計(jì)仿真與后端硬件測(cè)試緊密耦合,是德科技構(gòu)建了一個(gè)覆蓋RISC-V芯片全生命周期的驗(yàn)證閉環(huán)。這種方案能夠在實(shí)驗(yàn)室里重現(xiàn)復(fù)雜的場(chǎng)景,提早暴露問題并指導(dǎo)設(shè)計(jì)改進(jìn),避免流片后才發(fā)現(xiàn)紕漏而被迫修復(fù)。事實(shí)證明,借助仿真-實(shí)測(cè)閉環(huán),可以顯著降低開發(fā)風(fēng)險(xiǎn)和成本——例如在高速接口設(shè)計(jì)中,仿真階段鎖定優(yōu)化參數(shù)可減少一次PCB迭代。憑借深厚的技術(shù)積累,是德科技構(gòu)筑的這一完整驗(yàn)證鏈路,為RISC-V芯片從概念到落地保駕護(hù)航,幫助工程師大幅提升驗(yàn)證信心和效率。

對(duì)于芯粒測(cè)試,ADS仿真、去嵌、和物理層測(cè)試方案的結(jié)合顯得更加必要,下圖是芯粒測(cè)試的流程實(shí)例。

圖:芯粒測(cè)試的流程

PCIe、DDR、CXL、Ethernet、

電源/信號(hào)完整性測(cè)試場(chǎng)景概覽

RISC-V芯片要在各種應(yīng)用中可靠運(yùn)行,離不開對(duì)其高速接口和板級(jí)性能的嚴(yán)格測(cè)試。是德科技的方案廣泛覆蓋了主流接口標(biāo)準(zhǔn)和完整性驗(yàn)證需求,典型場(chǎng)景包括:

PCI Express (PCIe):無論是在數(shù)據(jù)中心將RISC-V處理器與GPU加速卡相連,還是在嵌入式設(shè)備中擴(kuò)展高速外設(shè),總線接口PCIe都是關(guān)鍵紐帶。是德科技提供從PCIe 1.0到最新6.0的物理層和協(xié)議層一致性測(cè)試方案,可對(duì)發(fā)射端眼圖和抖動(dòng)、信道插損和回?fù)p、接收端誤碼率等進(jìn)行全面測(cè)量。配套的協(xié)議分析儀和協(xié)議發(fā)生器則用于驗(yàn)證鏈路訓(xùn)練狀態(tài)機(jī)(LTSSM)、錯(cuò)誤處理等協(xié)議行為。借助如UXR系列示波器、M8000A系列誤碼儀、PNA/PNA-X/PNA-L矢量網(wǎng)絡(luò)分析儀及P5570A 和 P5573A PCIe 6.0 協(xié)議分析儀測(cè)試工具,工程師能夠高效完成PCIe鏈路的一致性認(rèn)證和調(diào)試,確保RISC-V芯片與現(xiàn)有PCIe生態(tài)無縫互通。

DDR內(nèi)存接口:RISC-V處理器廣泛用于高性能計(jì)算和AI加速時(shí),常需連接高速DDR/LPDDR內(nèi)存。是德科技的解決方案覆蓋DDR3/4/5及LPDDR5/6等標(biāo)準(zhǔn),從時(shí)鐘抖動(dòng)、信號(hào)眼圖、命令總線時(shí)序到電壓噪聲均有針對(duì)性的測(cè)試項(xiàng)目。通過高帶寬示波器配合DDR一致性測(cè)試軟件,可自動(dòng)化測(cè)量讀寫眼高/眼寬、時(shí)序參數(shù)(tDQSQ、tDQSCK等)是否達(dá)標(biāo);結(jié)合誤碼儀可以模擬加擾噪聲驗(yàn)證數(shù)據(jù)可靠性。此外,是德科技還提供前仿真到后測(cè)量的一體化DDR分析工具:IBIS模型仿真布線拓?fù)洌瑢?shí)測(cè)S參數(shù)比對(duì)仿真眼圖,幫助客戶在DDR接口設(shè)計(jì)中實(shí)現(xiàn)仿真-測(cè)試閉環(huán),平滑升級(jí)到新一代存儲(chǔ)器。

CXL高速互連:Compute Express Link (CXL)是新興的基于PCIe的緩存一致性互連,總線標(biāo)準(zhǔn)復(fù)雜且要求嚴(yán)格。針對(duì)采用CXL架構(gòu)的RISC-V 芯片,是德科技的PCIe5.0/6.0測(cè)試平臺(tái)同樣適用:能夠測(cè)量CXL鏈路的物理層信號(hào)質(zhì)量,并通過協(xié)議分析儀驗(yàn)證CXL的一致性協(xié)議(如內(nèi)存緩存一致性、設(shè)備內(nèi)存映射)是否正確實(shí)現(xiàn)。利用Keysight提供的PCIe/CXL協(xié)議觸發(fā)和解碼工具,可以在鏈路訓(xùn)練、讀寫事務(wù)中捕獲異常,確保RISC-V芯片在CXL互連下數(shù)據(jù)一致且延遲可控。

高速以太網(wǎng) (Ethernet):許多RISC-V應(yīng)用(例如網(wǎng)絡(luò)處理器、物聯(lián)網(wǎng)網(wǎng)關(guān)等)需要支持千兆乃至更高速率的以太網(wǎng)通信。是德科技具備從1GbE到400GbE/800GbE以太網(wǎng)物理層的一體化測(cè)試能力。通過誤碼儀和示波器相結(jié)合,可測(cè)試高速SERDES鏈路的誤碼率、抖動(dòng)容限和眼圖裕度;使用矢量網(wǎng)絡(luò)分析儀能評(píng)估高速差分線路的特性阻抗匹配和模式轉(zhuǎn)換。針對(duì)以太網(wǎng)標(biāo)準(zhǔn),還支持自動(dòng)一致性測(cè)試套件,覆蓋IEEE規(guī)范要求的電氣參數(shù)測(cè)試,幫助工程師快速判斷設(shè)計(jì)是否符合Ethernet標(biāo)準(zhǔn)。無論是板上走線還是光模塊接口,都可以在Keysight平臺(tái)上完成全面的物理層驗(yàn)證,為RISC-V芯片的網(wǎng)絡(luò)通信功能提供信心保障。

電源和信號(hào)完整性 (PI/SI):隨著芯片工藝和速率的提升,板級(jí)電源穩(wěn)定與信號(hào)質(zhì)量對(duì)系統(tǒng)性能的影響愈發(fā)突出。是德科技將PI/SI測(cè)試納入驗(yàn)證鏈路中,提供專門工具監(jiān)控和優(yōu)化這些“看不見”的細(xì)節(jié)。例如,通過高速示波器配合電源軌探頭,可以測(cè)量芯片供電的瞬態(tài)紋波噪聲,并使用專用分析軟件評(píng)估電源噪聲對(duì)高速數(shù)據(jù)眼圖的影響。在信號(hào)完整性方面,利用矢量網(wǎng)絡(luò)分析儀獲取走線的S參數(shù)后,工程師可以在ADS里仿真不同補(bǔ)償方案(如預(yù)加重、均衡),再將其應(yīng)用于實(shí)際電路驗(yàn)證效果。此外,Keysight提供抖動(dòng)/干擾注入工具,可在實(shí)驗(yàn)室重現(xiàn)極端干擾場(chǎng)景,檢驗(yàn)RISC-V芯片的抗擾裕度。通過這一系列軟硬件手段,電源和信號(hào)完整性問題能夠在設(shè)計(jì)早期就被發(fā)現(xiàn)并解決,確保最終產(chǎn)品在苛刻環(huán)境下依然穩(wěn)定工作。

綜上,是德科技構(gòu)建了覆蓋PCIe 1.0~6.0、DDR3~5/LPDDR6、Ethernet 400G/800G等各類高速接口,以及板級(jí)SI/PI性能的完整測(cè)試方案,涵蓋了從發(fā)送端、信道到接收端的全流程驗(yàn)證。通過模塊化的軟硬件組合,該方案幾乎囊括了RISC-V芯片可能涉及的所有測(cè)試場(chǎng)景,真正做到一站式保障芯片各方面指標(biāo)的符合性和可靠性。

結(jié)語:從開放指令集到驗(yàn)證閉環(huán)的落地路徑

開放的RISC-V指令集正為計(jì)算產(chǎn)業(yè)帶來創(chuàng)新活力,但要將這份潛力轉(zhuǎn)化為可靠的產(chǎn)品,完善的驗(yàn)證閉環(huán)至關(guān)重要。針對(duì)RISC-V芯片設(shè)計(jì)彈性大、驗(yàn)證難度高的特點(diǎn),是德科技以其專業(yè)測(cè)試測(cè)量能力打造了從仿真到測(cè)試的全覆蓋解決方案,彌合了設(shè)計(jì)預(yù)期與實(shí)際性能之間的鴻溝。在這種閉環(huán)驗(yàn)證思路的護(hù)航下,RISC-V芯片的開發(fā)風(fēng)險(xiǎn)大大降低,創(chuàng)新者們可以更大膽地探索定制化設(shè)計(jì)而無后顧之憂。

展望未來,RISC-V就像給算力生態(tài)開辟了一個(gè)“新接口”:它既能與現(xiàn)有的GPU、PCIe、以太網(wǎng)等體系協(xié)同合作,又能玩出指令級(jí)和架構(gòu)級(jí)定制的新花樣。隨著軟硬件生態(tài)日趨成熟,有了從設(shè)計(jì)到測(cè)試的閉環(huán)保障,RISC-V的落地之路將更加穩(wěn)健而快捷。或許再過幾年,我們?nèi)粘J褂玫氖謾C(jī)、電腦、智能汽車中都將出現(xiàn)RISC-V芯片的身影。是德科技將持續(xù)深耕測(cè)試測(cè)量技術(shù),攜手產(chǎn)業(yè)伙伴完善這一開放架構(gòu)的驗(yàn)證體系,加速邁向一個(gè)開放創(chuàng)新、閉環(huán)可靠的RISC-V新時(shí)代。

技術(shù)支持

相關(guān)文章

- 如何通過矢量網(wǎng)絡(luò)分析儀的紋波測(cè)試判斷傳輸線阻抗不連續(xù)性

- ATECLOUD如何快速準(zhǔn)確地進(jìn)行電源完整性測(cè)試?

- 如何使用頻譜分析儀測(cè)量放大器的1dB壓縮點(diǎn)

- 如何搭建基于鎖相放大器的微弱磁場(chǎng)檢測(cè)系統(tǒng)

- 頻譜分析儀如何導(dǎo)出數(shù)據(jù)到電腦

- Tektronix助力二維材料器件與芯片研究與創(chuàng)新

- 如何用阻抗分析儀精準(zhǔn)測(cè)量電荷轉(zhuǎn)移電阻

- 阻抗分析儀如何測(cè)電感的自諧振頻率

- 如何使用頻譜分析儀測(cè)量數(shù)字調(diào)制信號(hào)的EVM

- 如何使用阻抗分析儀測(cè)量陶瓷電容的頻率特性

相關(guān)產(chǎn)品

關(guān)注官方微信

關(guān)注官方微信